Data Flow Modelling in Verilog

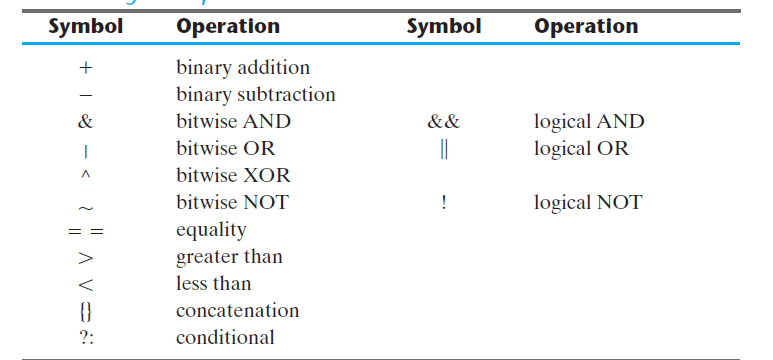

Verilog uses a 4 value logic value system so Verilog switch input and output signals can take any of the four 0 1 Z and X logic values. Besides them assignments using only operators AND NOT sll etc can also be used to construct code.

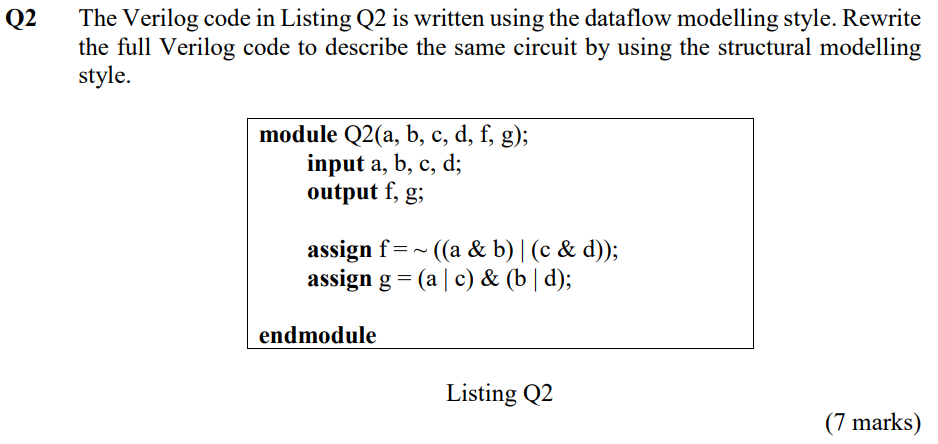

Solved The Verilog Code In Listing Q2 Is Written Using The Chegg Com

Behavioral modeling is the highest level of abstraction in the Verilog HDL.

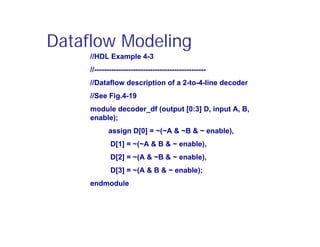

. Then we use assignment statements in data flow modeling. Meanwhile the graphics engine will execute post-processed data from the previous batch dumped into another part of memory and so on. The VLSI IC circuits design flow is shown in the figure below.

Module AND_2_data_flow output Y input A B. Verilog code for AND gate using data-flow modeling. AEDT provides access to the Ansys gold-standard electromagnetics simulation solutions such as Ansys HFSS Ansys Maxwell Ansys Q3D Extractor Ansys SIwave and Ansys Icepak using electrical CAD ECAD and mechanical CAD MCAD.

A comprehensive resource on Verilog HDL for beginners and experts large and complicated digital circuits can be incorporated into hardware by using Verilog a hardware description language HDL. We would again start by declaring the module. Led by some of our top Senior Traders the program includes option theory systems training trading strategy risk management data analysis quant modeling and hands-on trading simulations.

Describes how the Vitis development environment lets you build a software application using the OpenCL API to run hardware kernels on accelerator cards like a Xilinx Alveo Data Center accelerator card for FPGA-based acceleration. In this modeling style the flow of data through the entity is expressed using concurrent parallel signal. All that a designer need is the.

The various levels of design are numbered and the blocks show processes in the design flow. Junior Traders then graduate into real-time trading rotations and a one-on-one mentorship with a Senior Trader. Ansys Electronics Desktop AEDT The Ansys Electronics Desktop AEDT is a platform that enables true electronics system design.

Switch Level Primitives Switches are unidirectional or bidirectional and resistive or non-resistive for each group those primitives that switch on with a positive gate such as NMOS transistor and those. They also decide on how the data should flow inside the chip. Specifications comes first they describe abstractly the functionality interface and the architecture of the digital IC circuit to be designed.

Week-6Switch level modelling Week-7Synthesis of combinational logic using verilog Week-8Synthesis of sequential logic. The concurrent statements in VHDL are WHEN and GENERATE. Computer-aided diagnosis deep learning applications in image analysis multimedia information retrieval imaging informatics for healthcare research and applications biomedical imaging and visualization biomedical image datasets representation of pictorial data visualization feature extraction segmentation image guided surgery and intervention texture shape and motion.

An example would be the data flow when a processor fetches imaging data from the system ram and executes them.

What Is The Difference Between Data Flow And Behavioral Modelling In Verilog Hdl Ee Vibes

Veriloghdl Basic Data Flow Modelling Youtube

Lecture 4 Dataflow And Behavioral Modeling I Youtube

Data Flow Modeling Verilog Hdl Lecture Slides Slides Verilog And Vhdl Docsity

Verilog Part 1 Example Dataflow And Structural Description Youtube

0 Response to "Data Flow Modelling in Verilog"

Post a Comment